# AS5003 Arcadium™ I2C Programmable Oscillator, 10 kHz to 350 MHz

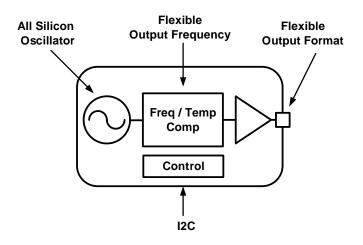

The AS5003 Arcadium™ all-silicon oscillator utilizes proprietary frequency synthesis and sensor technologies to provide a quartz-free, MEMS-free, low jitter clock at any output frequency. The device is fully programmable to any frequency from 10 kHz to 350 MHz with < 0.026 ppb resolution and maintains low jitter across its operating range. The AS5003 uses on-chip temperature and strain sensors, and an advanced LC tank architecture to achieve excellent reliabilities even in high impact shock scenarios.

AS5003's on-chip power supply filtering provides industry-leading power supply noise rejection, simplifying the task of generating low jitter clocks in noisy systems that use switched-mode power supplies. Offered in a variety of industry-standard packages, the AS5003 has a dramatically simplified supply chain that enables Aeonsemi to ship samples shortly after receipt of order. The AS5003 is user-configurable with an I<sup>2</sup>C interface for a wide variety of user specifications, including frequency, output format, and DCO mode. Default configuration is factory programmed at time of shipment. It also guarantees 100% electrical testing of every device before shipment.

#### **KEY FEATURES**

- Quartz-free and MEMS-free without mechanical moving parts

- · I2C programmable to any frequency

- · Differential: 10 kHz to 350 MHz

- LVCMOS: 10 kHz to 212.5 MHz

- Up to 0.026 ppb frequency tuning resolution

- I2C interface supports 100 kbps, 400 kbps and 1 Mbps (Fast Mode Plus)

- Low jitter: 350 fs Typ RMS (12 kHz 20 MHz)

- Compliant to PCIe Gen 1/2/3/4/5 jitter requirements

- 50 ppm stability (-40 to 105°C)

- Integrated LDO for on-chip power supply noise filtering

- Support continuous 1.8V to 3.3V  $\ensuremath{V_{\text{DD}}}$  supply operation

- LVPECL, LVDS, CML, HCSL, CMOS, and Dual CMOS output options

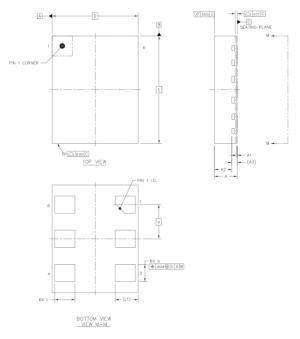

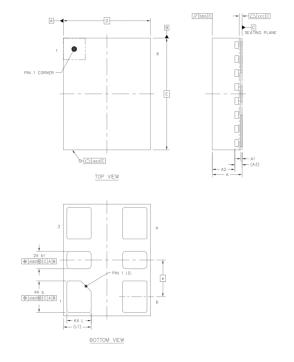

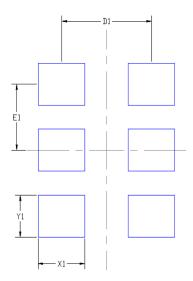

- Industrial standard 3.2 x 5, 2.5 x 3.2 mm package footprints

### **APPLICATIONS**

- · 1G/10G/40G/100G Ethernet

- Servers, switches, storage, NICs, search acceleration

- · Test and measurement

- · Clock and data recovery

- · FPGA/ASIC clocking

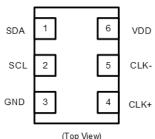

### **Pin Assignments**

(LVPECL/LVDS/HCSL/CML/Dual CMOS)

3.2 x 5 mm and 2.5 x 3.2 mm

| Pin # | Descriptions                        |  |  |  |  |

|-------|-------------------------------------|--|--|--|--|

| 1     | SDA = I <sup>2</sup> C Serial Data  |  |  |  |  |

| 2     | SCL = I <sup>2</sup> C Serial Clock |  |  |  |  |

| 3     | GND = Ground                        |  |  |  |  |

| 4     | CLK+ = Clock output                 |  |  |  |  |

| 5     | CLK- = Complementary clock output   |  |  |  |  |

| 6     | V <sub>DD</sub> = Power supply      |  |  |  |  |

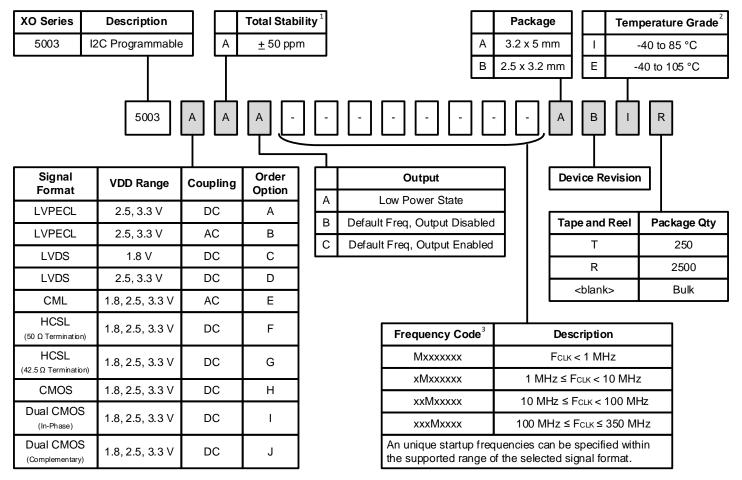

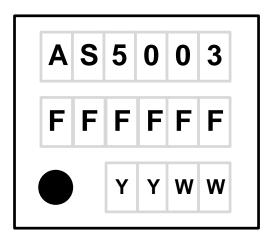

# 1. Ordering Guide

The AS5003 Oscillator supports a variety of initial options including frequency, output format, as shown in the chart below. Configurations are changeable by users via I2C interface upon startup. Samples are available in 2 weeks.

#### Notes:

- 1. Total stability includes temp stability, initial accuracy, load pulling, V<sub>DD</sub> variation, and 10 years aging at 40 °C.

- 2. Device supports extended industrial temperature range of -40 to 105°C only with  $V_{DD} = 1.8V$  (+/- 5%).

- 3. For example: 156.25 MHz = 156M2500; 25 MHz = 25M00000.

# 2. Electrical Specifications

# **Table 2.1 Electrical Specifications**

$V_{DD}$  = 1.8 V, 2.5 or 3.3 V ± 5%,  $T_A$  = -40 to 85 °C;  $V_{DD}$  = 1.8 V ± 5%,  $T_A$  = -40 to 105 °C

| Parameter                                      | Symbol                         | Test Condition/Comment                                                               | Min                    | Тур  | Max                    | Unit            |

|------------------------------------------------|--------------------------------|--------------------------------------------------------------------------------------|------------------------|------|------------------------|-----------------|

| Temperature Range                              | T <sub>A</sub>                 |                                                                                      | -40                    | _    | 105                    | °C              |

| Frequency Range                                | F <sub>CLK</sub>               | LVPECL, LVDS, CML, HCSL                                                              | 0.01                   | _    | 350                    | MHz             |

|                                                |                                | CMOS, Dual CMOS                                                                      | 0.01                   | _    | 212.5                  | MHz             |

| Supply Voltage                                 | V <sub>DD</sub>                |                                                                                      | 1.71                   |      | 3.47                   | V               |

| Supply Current                                 | I <sub>DD</sub>                | Tristate Hi-Z (output disabled)                                                      | _                      | 40   | 50                     | mA              |

| $(F_{CLK} = 50 \text{ MHz})$                   |                                | Ready State                                                                          | _                      | 1    | 2                      | mA              |

|                                                |                                | LVPECL (DC-Coupled)                                                                  | _                      | 70   | 80                     | mA              |

|                                                |                                | LVPECL (AC-Coupled)                                                                  | _                      | 60   | 70                     | mA              |

|                                                |                                | LVDS                                                                                 | _                      | 45   | 55                     | mA              |

|                                                |                                | HCSL                                                                                 | _                      | 60   | 70                     | mA              |

|                                                |                                | CML                                                                                  | _                      | 60   | 70                     | mA              |

|                                                |                                | CMOS                                                                                 | _                      | 40   | 55                     | mA              |

|                                                |                                | Dual CMOS                                                                            | _                      | 50   | 60                     | mA              |

| Total Stability <sup>1</sup>                   | F <sub>STAB</sub>              | Frequency stability                                                                  | -50                    | _    | 50                     | ppm             |

| Rise/Fall Time                                 | T <sub>R</sub> /T <sub>F</sub> | LVPECL/LVDS/CML                                                                      | _                      | _    | 350                    | ps              |

| (20% to 80% V <sub>PP</sub> )                  |                                | CMOS / Dual CMOS<br>(C <sub>L</sub> = 5 pF)                                          | _                      | 0.5  | 1.5                    | ns              |

|                                                |                                | HCSL, F <sub>CLK</sub> >50 MHz                                                       | _                      | _    | 550                    | ps              |

| Duty Cycle                                     | D <sub>C</sub>                 | All formats                                                                          | 45                     | _    | 55                     | %               |

| Output Enable (OE) <sup>2</sup>                | V <sub>IH</sub>                |                                                                                      | 0.7 × VDD              | _    | _                      | V               |

|                                                | V <sub>IL</sub>                |                                                                                      | _                      | _    | 0.3 × VDD              | V               |

|                                                | T <sub>D</sub>                 | Output Disable Time,<br>FCLK >10 MHz                                                 | _                      | _    | 0.5                    | μs              |

|                                                | T <sub>E</sub>                 | Output Enable Time,<br>FCLK >10 MHz                                                  | _                      | _    | 0.5                    | μs              |

| Powerup Time                                   | t <sub>OSC</sub>               | Time from $0.9 \times V_{DD}$ until output frequency (F <sub>CLK</sub> ) within spec | _                      | _    | 4                      | ms              |

| LVPECL Output Option <sup>3</sup>              | V <sub>oc</sub>                | Mid-level                                                                            | V <sub>DD</sub> – 1.55 | _    | V <sub>DD</sub> – 1.25 | V               |

| (DC-Coupled)                                   | Vo                             | Swing (diff)                                                                         | 1.4                    | _    | 1.85                   | $V_{PP}$        |

| LVPECL Output Option <sup>3</sup> (AC-Coupled) | Vo                             | Swing (diff)                                                                         | 1.4                    |      | 1.85                   | V <sub>PP</sub> |

| LVDS Output Option <sup>4</sup>                | V <sub>oc</sub>                | Mid-level (2.5 V, 3.3 V V <sub>DD</sub> )                                            | 1.125                  | 1.20 | 1.275                  | V               |

| (DC-Coupled)                                   |                                | Mid-level (1.8 V V <sub>DD</sub> )                                                   | 0.795                  | 0.85 | 0.905                  | V               |

|                                                | Vo                             | Swing (diff)                                                                         | 0.5                    | 0.82 | 0.96                   | V <sub>PP</sub> |

| Parameter                                   | Symbol          | Test Condition/Comment                        | Min                    | Тур | Max                    | Unit     |

|---------------------------------------------|-----------------|-----------------------------------------------|------------------------|-----|------------------------|----------|

| HCSL Output Option <sup>4</sup>             | V <sub>OH</sub> | Output voltage high                           | 695                    | 815 | 935                    | mV       |

| $(R_{term} = 50 Ω; DC-Coupled)$             | V <sub>OL</sub> | Output voltage low                            | 0                      | 5   | 10                     | mV       |

| HCSL Output Option <sup>5</sup>             | V <sub>OH</sub> | Output voltage high                           | 695                    | 820 | 945                    | mV       |

| $(R_{term} = 42.5 Ω; DC-Coupled)$           | V <sub>OL</sub> | Output voltage low                            | 0                      | 5   | 10                     | mV       |

| CML Output Option <sup>4</sup> (AC-Coupled) | Vo              | Swing (diff)                                  | 0.725                  | 0.8 | 0.89                   | $V_{PP}$ |

| CMOS Output Option                          | V <sub>OH</sub> | $I_{OH} = 8/6/4$ mA for 3.3/2.5/1.8V $V_{DD}$ | 0.83 × V <sub>DD</sub> | _   | _                      | V        |

|                                             | V <sub>OL</sub> | $I_{OL} = 8/6/4$ mA for 3.3/2.5/1.8V $V_{DD}$ | _                      | -   | 0.17 × V <sub>DD</sub> | V        |

## Notes:

- 1. Total Stability includes temperature stability, initial accuracy, load pulling, V<sub>DD</sub> variation, and aging for 10 years at 40 °C.

- 2. The  $T_D$  and  $T_E$  < 10 ns + 3 \* 1/ $F_{CLK}$  for all frequencies measured from the end of the I<sup>2</sup>C byte write to OE control registers.

- 3.  $R_{term}$  = 50  $\Omega$  to  $V_{DD}$  2.0 V (see Figure 4.1).

- 4.  $R_{term}$  = 100  $\Omega$  (differential) (see Figure 4.2).

- 5.  $R_{term}$  = 42.5  $\Omega$  or 50  $\Omega$  to GND (see Figure 4.3).

# Table 2.2: I<sup>2</sup>C Characteristics

$V_{DD}$  = 1.8 V, 2.5 or 3.3 V ± 5%,  $T_A$  = -40 to 85 °C;  $V_{DD}$  = 1.8 V ± 5%,  $T_A$  = -40 to 105 °C

| Parameter                                                                 | Symbol           | Test Condition/Comment            | Min  | Тур   | Max  | Unit |

|---------------------------------------------------------------------------|------------------|-----------------------------------|------|-------|------|------|

| Frequency Reprogramming Resolution                                        | V <sub>RES</sub> |                                   | _    | 0.026 | _    | ppb  |

| Frequency Range for Small Frequency Change (Continuous Glitchless Output) |                  | From center frequency             | -970 |       | +970 | ppm  |

| Settling Time for Small Frequency Change (DCXO Feature)                   |                  | < ± 970 ppm from center frequency |      |       | 8    | us   |

| Settling Time for Frequency Change (fUSER_FREQ Register)                  |                  |                                   |      |       | 200  | us   |

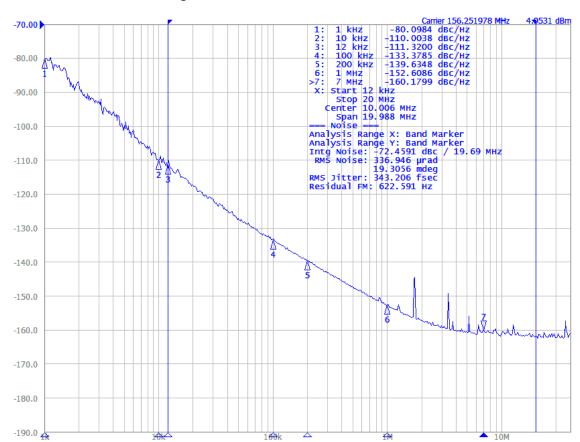

## Table 2.3: Clock Output Phase Jitter and PSRR

$V_{DD}$  = 1.8 V, 2.5 or 3.3 V ± 5%,  $T_A$  = -40 to 85 °C;  $V_{DD}$  = 1.8 V ± 5%,  $T_A$  = -40 to 105 °C

| Parameter                                          | Symbol | Test Condition/Comment              | Min | Тур | Max | Unit |  |  |  |

|----------------------------------------------------|--------|-------------------------------------|-----|-----|-----|------|--|--|--|

| Phase Jitter (RMS, 12 kHz - 20 MHz) <sup>1,2</sup> | фл     | φ <sub>J</sub> Differential Formats |     | 350 | 750 | fs   |  |  |  |

| F <sub>CLK</sub> ≥ 10 MHz                          |        | CMOS, Dual CMOS                     | _   | 350 | _   | fs   |  |  |  |

| Phase Jitter (RMS, 50 kHz - 20 MHz)                | фл     | Differential Formats                | _   | 150 | 250 | fs   |  |  |  |

| F <sub>CLK</sub> ≥ 156.25 MHz                      |        | CMOS, Dual CMOS                     | _   | 100 | _   | fs   |  |  |  |

| Spurs Induced by External Power Supply             | PSRR   | 100 kHz sine wave                   | _   | -76 | _   |      |  |  |  |

| Noise, 50 mVpp Ripple.  LVDS 156.25 MHz Output     |        | 200 kHz sine wave                   |     | -75 | _   | dD.a |  |  |  |

| V <sub>DD</sub> = 1.8 V                            |        | 500 kHz sine wave                   | _   | -75 | _   | dBc  |  |  |  |

|                                                    |        | 1 MHz sine wave                     | _   | -75 | _   | _    |  |  |  |

| Spurs Induced by External Power Supply             | PSRR   | 100 kHz sine wave                   | _   | -83 | _   |      |  |  |  |

| Noise, 50 mVpp Ripple.  LVDS 156.25 MHz Output     |        | 200 kHz sine wave                   | _   | -83 | _   | dBc  |  |  |  |

| V <sub>DD</sub> = 2.5 or 3.3 V                     |        | 500 kHz sine wave                   | _   | -83 | _   | abc  |  |  |  |

|                                                    |        | 1 MHz sine wave                     | _   | -82 | _   |      |  |  |  |

### Note:

- 1. Applies to output frequency: 50, 100, 156.25, 212.5, 350 MHz

- 2. Guaranteed by characterization. Jitter inclusive of any spurs

Figure 2.1: Phase Noise at 156.25 MHz

Table 2.4: Environmental Compliance and Package Information

| Parameter                  | Test Condition |

|----------------------------|----------------|

| Moisture Sensitivity Level | 1              |

### Note:

For additional product information not listed in the data sheet (e.g. RoHS Certifications, MSDS data, qualification data, REACH Declarations, ECCN codes, etc.), contact <a href="mailto:aeonsemi.com/contact-us/">aeonsemi.com/contact-us/</a>

**Table 2.5: Thermal Conditions**

| Package                  | Parameter                              | Symbol | Test Condition | Value | Unit |

|--------------------------|----------------------------------------|--------|----------------|-------|------|

| 2 2 v 5 mm               | Thermal Resistance Junction to Ambient | ΘЈА    | Still Air      | 105   | °C/W |

| 3.2 x 5 mm,<br>6-pin DFN | Thermal Resistance Junction to Board   | ΘЈВ    | Still Air      | 81    | °C/W |

| ·                        | Max Junction Temperature               | TJ     | Still Air      | 125   | °C   |

| 2.5 x 3.2 mm,            | Thermal Resistance Junction to Ambient | ΘЈΑ    | Still Air      | 108   | °C/W |

| 6-pin DFN                | Thermal Resistance Junction to Board   | ΘЈВ    | Still Air      | 84    | °C/W |

|                          | Max Junction Temperature               | TJ     | Still Air      | 125   | °C   |

## Table 2.6: Absolute Maximum Ratings<sup>1</sup>

| Parameter                                     | Symbol            | Rating                        | Unit |

|-----------------------------------------------|-------------------|-------------------------------|------|

| Maximum Operating Temperature <sup>2</sup>    | T <sub>AMAX</sub> | 105                           | °C   |

| Storage Temperature                           | T <sub>S</sub>    | -55 to 125                    | °C   |

| Supply Voltage                                | V <sub>DD</sub>   | -0.5 to 3.8                   | V    |

| Input Voltage                                 | V <sub>IN</sub>   | -0.5 to V <sub>DD</sub> + 0.3 | V    |

| ESD HBM (JESD22-A114)                         | НВМ               | 4.0                           | kV   |

| Solder Temperature <sup>3</sup>               | T <sub>PEAK</sub> | 260                           | °C   |

| Solder Time at T <sub>PEAK</sub> <sup>3</sup> | T <sub>P</sub>    | 20 - 40                       | sec  |

## Notes:

- 1. Stresses beyond those listed in this table may cause permanent damage to the device. Functional operation specification compliance is not implied at these conditions. Exposure to maximum rating conditions for extended periods may affect device reliability.

- 2. For  $V_{DD} = 1.8V$  only; otherwise 85°C.

- 3. The device is compliant with JEDEC J-STD-020.

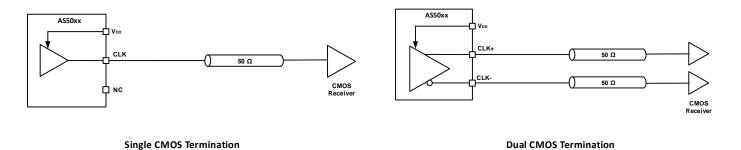

# 3. CMOS Buffer and Output Terminations

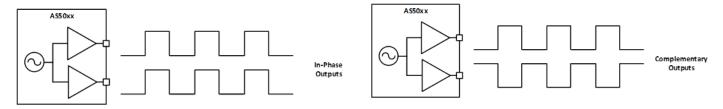

Dual CMOS output format ordering options support either complementary or in-phase signals for two identical frequency outputs. This feature enables replacement of multiple XOs with a single AS5003 device.

Figure 3.1: Integrated 1:2 CMOS Buffer Supports In-Phase or Complementary Outputs

Figure 3.2: CMOS Output Terminations

# 4. Recommended Output Terminations

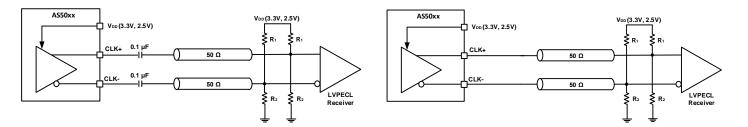

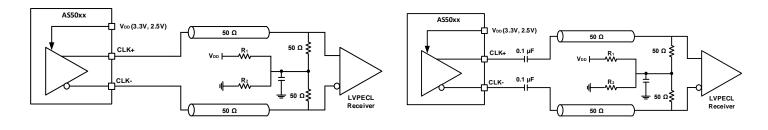

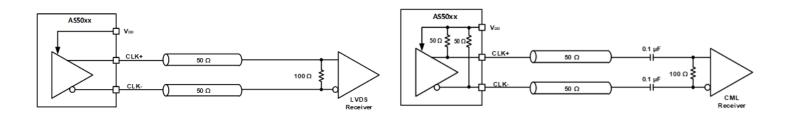

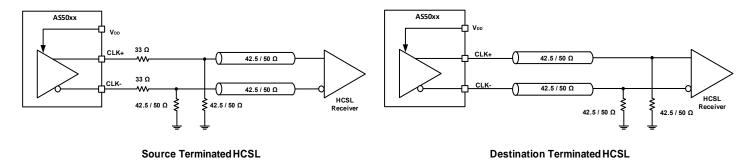

The output drivers support AC-coupled or DC-coupled terminations as shown in figures below.

AC-Coupled LVPECL - Thevenin Termination

DC-Coupled LVPECL – 50  $\Omega$  w/ VTT Bias

DC-Coupled LVPECL - Thevenin Termination

AC-Coupled LVPECL –  $50 \Omega$  w/ VTT Bias

| Termination Resistor Values |       |        |  |  |  |  |  |

|-----------------------------|-------|--------|--|--|--|--|--|

| V <sub>DD</sub>             | R1    | R2     |  |  |  |  |  |

| 3.3 V                       | 127 Ω | 82.5 Ω |  |  |  |  |  |

| 2.5 V                       | 250 Ω | 62.5 Ω |  |  |  |  |  |

Figure 4.1: LVPECL Output Terminations

DC-Coupled LVDS AC-Coupled CML

Figure 4.2: LVDS / CML Output Terminations

Figure 4.3: HCSL Output Terminations

# 5. Configuring via I<sup>2</sup>C Interface

### 5.1 I2C Serial Interface

The I<sup>2</sup>C interface on the AS5003 is fully compatible with the "UM10204 I<sup>2</sup>C-bus specification and user manual, Rev. 6 - 4 April 2014" standard, as described in Table 5.1.

Table 5.1: I<sup>2</sup>C compatibility

| I2C      | Speed   | Compliance | Notes                                                                                               |

|----------|---------|------------|-----------------------------------------------------------------------------------------------------|

| Standard | 100 kHz | Compliant  | N/A                                                                                                 |

| Fast     | 400 kHz | Compatible | SDA failing edge can be faster than 20 ns depending on loading                                      |

| Fast+    | 1 MHz   | Compatible | SDA falling edge can be faster than 20 ns depending on loading.  SDA max pull down current is 6 mA. |

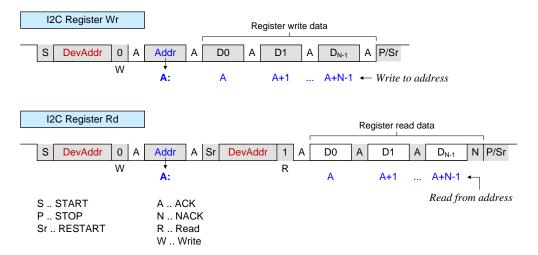

### 5.2 I<sup>2</sup>C Register Write and Read Protocol

AS5003 implements an 8-bit I<sup>2</sup>C address space with 256 addressable byte register locations. Certain device register and bits are reserved, and they must not be changed from their default reset state.

In an I<sup>2</sup>C bus system, the AS5003 acts as a slave device connected to the I<sup>2</sup>C serial interface bus. It is accessed via a 7-bit factory programmed (per user specification) slave address. Allowed values of this device address are in the range from 16 to 119. Both write and read register transactions with register address autoincrement are enabled as shown in *Figure 5.1*.

Figure 5.1: I<sup>2</sup>C write and read transactions

Write register transaction is an I<sup>2</sup>C write transaction with an 8-bit register address data byte stream. It is followed by one or more register data bytes. Read register sequence starts after a write transaction to set the read register address. It is followed by the I<sup>2</sup>C read transaction to read one or more data bytes.

The register address autoincrement is enabled upon power up. It is incremented till a maximum address 0xFF of the I<sup>2</sup>C register space is reached.

The register address autoincrement is disabled by writing register bl2C\_INC\_DIS=1 and re-enabled again by writing bl2C\_INC\_DIS=0. During this process, all bytes in the I<sup>2</sup>C transactions are written to or read from a set address. Having the register autoincrement disabled is required for a DCXO streaming mode.

Data and address bytes appear on the SDA bus with the most significant bit (MSB) first per I<sup>2</sup>C standard. During I<sup>2</sup>C transactions, SCL clock bus is never stalled by the device.

#### 5.3 Device Operation

After an initial power up sequence, the device operates in either Ready state or an Active state depending on customization in factory. The Ready state is a power down standby state when majority of internal circuitries are powered down. The **Active** state is the device active mode with all internal circuitries powered up. Writing to register bUSYS\_CTRL can move the device between Ready state and Active state.

The following three power up options are available for factory configuration:

- 1. Ready state: The device is in the power down standby mode. Writing transaction to register bUSYS\_CTRL is required to enable the device and enable the Active state.

- 2. Active state with bODIV\_CTRL=0: The device generates frequency internally, but output is disabled. Writing transaction to register bODIV\_CTRL is required to enable output driver to propagate output frequency.

- 3. Active state with bODIV\_CTRL=1: The device is fully functional, and output is enabled. I<sup>2</sup>C intervention is not necessary.

In the state 1 and 2 above, user can write to  $I^2C$  to change drive mode or central frequency from the factory set values prior to enabling the device output or before moving to Active state.

## 5.4 Changing Frequency and Output Driver Mode

After startup, the device is at the factory set frequency, output driver mode, and device state. The device is ready to be controlled by I<sup>2</sup>C register writes. All register writes can take immediate effect, except fUSER\_FREQ and bDRV\_MODE registers which require a follow on Apply command. User frequency register, "fUSER\_FREQ", is a 4-byte big endian register representing frequency as a binary32 IEEE 754-2008 standard number, in [Hz] units. User driver mode register, "bDRV\_MODE" is a single byte number representing driver mode described in Table 5.19.

Changing frequency and driver mode requires two steps:

- Writing fUSER\_FREQ and/or bDRV\_MODE registers with the new desired central frequency and/or driver mode. Only the changing register needs to be written. Writing order in bytes is not essential. Writing these registers only records the new values, but does not invoke any internal processing.

- 2. Writing bUSYS\_CTRL register with one of four Apply\* commands. Once the Apply\* command is accepted, the device uses the fUSER\_FREQ and bDRV\_MODE register values and invokes internal central frequency and/or driver mode.

Changing frequency can be completed by either disabling the output driver or keeping the output drive enabled. This is determined by applying different Apply\* commands. The bUSYS\_CTRL values and descriptions are shown in *Table 5.2*.

| Value  | Mnemonic              | Description                                                                                                                       | stat_busy |

|--------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------|-----------|

| 0      | UsysNop               | No operation                                                                                                                      |           |

| 1      | UsysReady             | Ready standby power down state                                                                                                    |           |

| 2      | UsysActive            | Active state                                                                                                                      |           |

| 3      | <reserved></reserved> | No operation                                                                                                                      |           |

| 4      | UsysRstSys            | Invoke system reset restart                                                                                                       |           |

| 5      | UsysRstPor            | Invoke power-on reset restart                                                                                                     |           |

| 6      | <reserved></reserved> | Do not use                                                                                                                        |           |

| 7      | <reserved></reserved> | Do not use                                                                                                                        |           |

| 8      | UsysApply             | Apply: Disable output if active, update only changed frequency/driver mode                                                        | Check/Set |

| 9      | UsysApplyForce        | Apply force: Disable output if active, force frequency/driver mode update                                                         | Check/Set |

| 10     | UsysApplyAct          | Apply active: Keep output running if active, update only changed frequency/driver mode                                            | Check/Set |

| 11     | UsysApplyActForce     | Apply active force: Keep output running if active, force frequency/driver mode update                                             | Check/Set |

| 12     | UsysRefresh           | Refresh: Refresh fUSER_FREQ and bDRV_MODE register values to reflect the actual current device frequency and driver mode settings | Check/Set |

| Others | <reserved></reserved> | Do not use                                                                                                                        |           |

Table 5.2: System control register bUSYS\_CTRL

Writing to "bUSYS\_CTRL" register generates an acceptance request. When this command is accepted, the "bUSYS\_CTRL" register is cleared. If a read from "bUSYS\_CTRL" returns a non-zero value, it means that the writing command is still waiting to be accepted. A command acceptance happens in less than 5 us from the finishing of writing to the "bUSYS\_CTRL" register. An accepted command can be either processed or ignored.

Commands other than "Apply\*" and "Refresh" are always processed after the acceptance. It is possible to interrupt any "Apply\*" or "Refresh" command under processing. A processing time depends on the command and its current state of the device, in most cases it is 1 ~ 5 us, but can be up to 160 us when the command is generated in the middle of the frequency change.

"Apply\*" and "Refresh" commands are only processed when "bUSYS\_STATS.stat\_busy" = 0. When "bUSYS\_STATS.stat\_busy" = 1, although new "Apply\*" and "Refresh" commands are accepted, they are ignored. The "bUSYS\_STATS.stat\_busy" = 1 status bit is the beginning of internal processing. The "bUSYS\_STATS.stat\_busy" = 0 occurs after this internal processing finishes. Changing frequency and output driver must be completed before invoking a new command.

Issuing a "Refresh" command reset the values of registers to match the actual state of the device. During a normal operation, the device keeps the values of fUSER\_FREQ and bDRV\_MODE synchronized with the internal state of the device. Reading these registers represent the actual frequency and output driver mode. However, the values could be different if writing occurs before applying the "Apply\*" or "Refresh" command. If the "Apply\*" command is not applied, then the registers value are the previous written values. Thus, issuing the "Refresh" command is necessary.

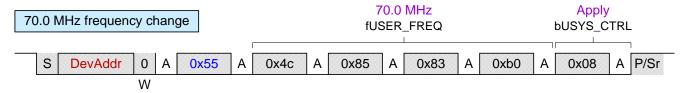

"fUSER\_FREQ" and "bUSYS\_STAT" registers are located back to back in I<sup>2</sup>C address space. As a result, the most used operation is done in a single I<sup>2</sup>C transaction as shown in Figure 5.2. This example shows changing the frequency to a 70 MHz, which corresponds a 32-bit floating point number, 0x4c8583b0 in [Hz]. It is followed by a "**Apply**" command to invoke the internal frequency update, and assumed that the I<sup>2</sup>C register address autoincrement is enabled, which is a default.

Figure 5.2: Frequency change I<sup>2</sup>C transaction

### 5.5 System Status

"bUSYS\_STAT" is a read only system status register. It is readable any time and it reflects the current device status. All possible values of the register are listed in *Table 5.3*.

|           | ŀ   | oUSYS | S_STA      | T        |           |              |            |                                       |

|-----------|-----|-------|------------|----------|-----------|--------------|------------|---------------------------------------|

| stat_busy | 1   | 1     | stat_trans | stat_rst | stat_tune | stat_actifve | stat_ready | Description                           |

| [7]       | [6] | [5]   | [4]        | [3]      | [2]       | [1]          | [0]        |                                       |

| 0         | 0   | 0     | 0          | 0        | 0         | 0            | 0          | Start up                              |

| V         | 0   | 0     | 0          | 0        | 0         | 0            | 1          | Ready state                           |

| V         | 0   | 0     | 0          | 0        | 0         | 1            | 0          | Active state                          |

| V         | 0   | 0     | 0          | 0        | 1         | 1            | 0          | Active state, tuning to new frequency |

| V         | 0   | 0     | 1          | 0        | 0         | 0            | 1          | Ready → Active transition             |

| V         | 0   | 0     | 1          | 0        | 0         | 1            | 0          | Active → Ready transition             |

| 0         | 0   | 0     | 1          | 1        | 0         | 0            | 0          | Reset processing, shutting down       |

| 0         | 0   | 0     | 0          | 1        | 0         | 0            | 0          | Reset accepted                        |

Table 5.3: System status bUSYS\_STAT register values

stat\_busy bit [7] value v denotes value 0 or 1. The bit is 1 at the beginning of Apply\* and Refresh commands internal processing and is 0 when the processing is done.

## **5.6 Output Drive Control**

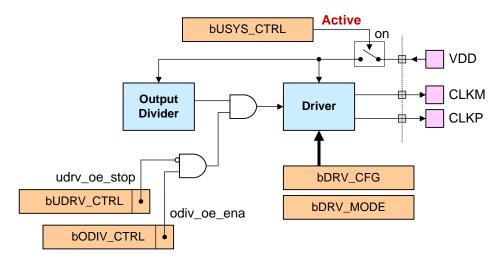

The output driver is powered up only in an **Active** state. CLKP and CLKM output signals are enabled or disabled by OE control register bits, "bUDRV\_CTRL.udrv\_oe\_stop" and "bODIV\_CTRL.odiv\_oe\_ena". The simplified control flow of output driver is shown in *Figure* 5.3.

Figure 5.3: Driver control flow

Putting system to Ready state or disabling the driver with "bDRV\_MODE" = 0 to issue one of the "Apply\*" commands power down the output driver.

### 5.7 Center Frequency Control

Changing "fUSER\_FREQ" register value controls the center frequency. The step does not apply to the DCXO feature.

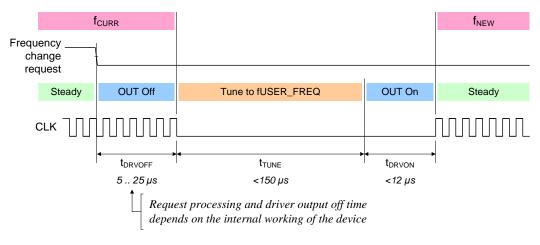

Frequency change request shown in *Figure 5.4* and *Figure 5.5* marks the time when a "Apply\*" command is written to a "bUSYS CTRL" register which corresponds with the write of the last data bit to this "bUSYS CTRL" register.

Figure 5.4 shows a timing of frequency change by using "Apply" command when a "fUSER\_FREQ" register value is different from the current frequency; or using "ApplyForce" command with the output disabled during the frequency change.

Figure 5.4: Frequency change by "Apply" command

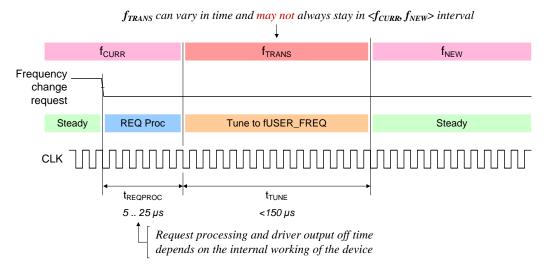

Figure 5.5 shows either using an "ApplyAct" command when a "fUSER\_FREQ" register has different value from the current frequency; or using an "ApplyActForce" command when the output keeps active during the frequency change. No signal glitches at the output occurs during the frequency change. However, there could be some periods in the output frequency corresponding when the current frequency and new frequency interval are not aligned. This behavior is device dependent and it also depends on the actual values and relationships in between the current and new frequencies.

Figure 5.5: Frequency change by "ApplyAct" command

#### 5.8 DCXO Control

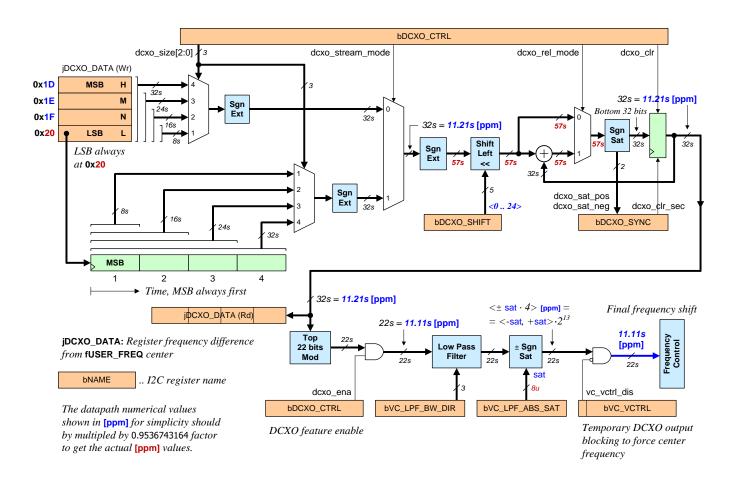

The device incorporates a Digital Controlled Oscillator (DCXO) feature to allow seamless and fast setting of the frequency deviation from the center frequency. It implements a 32-bit signed "jDCXO\_DATA" register in 11.21s signed bit format, which represents frequency offset from the current center frequency in "fUSER\_FREQ" register in [0.9536743164 ppm] units. The [ppm] is a frequency step equal to  $10^{-6}$  \* fUSER\_FREQ in [Hz]. The scaling factor is  $0.9536743164 = 10^{6}/2^{20}$ . It is possible to move the output frequency from the center frequency within the range  $\pm 975$  ppm.

The DCXO feature must be configured before writing to "bDCXO\_CTRL" and "bDCXO\_SHIFT" registers with an additional optional configuration, which is provided by "bVC\_LPF\_BW\_DIR" and "bVC\_LPF\_ABS\_SAT" registers. When a new frequency offset register "jDCXO\_DATA" is written, the output signal changes to a new frequency seamlessly and glitchlessly. The settlement time of a new output frequency from the end of last data bit of the byte written to a "bDCXO\_DATAL" register is less than 8 us.

The DCXO data path configuration is schematically shown in *Figure 5.6*. Numerical values are shown in "**NN.MMs**" notation where "NN" is the number of MSB bits representing integer part of the number, while MM represents number of LSB bits representing fractional part of the number. The letter '**s**' means signed, and the letter '**u**' is unsigned value. Signed values are represented in binary 2's complement. The values are labeled in [ppm] in *Figure 5.6* for simplicity. The numerical binary values must be multiplied by the factor of 0.9536743164 to represent the real [ppm] frequency offset value from the current center frequency.

Writing to a 32-bit "jDCXO\_DATA" register normally requires an I<sup>2</sup>C transaction of 6 bytes. Every update of the DCXO value would take 6 byte writing on an I<sup>2</sup>C bus, which takes ~56 us if using an I<sup>2</sup>C Fast+ with 1 MHz speed, or ~140 us if using an I<sup>2</sup>C Fast 400 kHz speed. In some applications, faster update speed may be required while the full 32-bit frequency offset resolution is not needed. To accommodate faster DCXO offset updates using I<sup>2</sup>C, the DCXO has the following configurable features:

- 1. Data size: bDCXO\_CTRL.dcxo\_size = {0|1|2|3|4} Select to write only 1, 2, 3, or all 4 bytes signed numbers, 0 means 4.

- Left shift: bDCXO\_SHIFT = <0, 24> range

Configurable shift of the entered input value to the left with up to 24 bits to scale small numbers to proper position within 32 bit number.

- 3. Data input:

Direct register mode: bDCXO\_CTRL.dcxo\_stream\_mode = 0 Write an input value to the jDCXO\_DATA bytes directly

Streaming mode: bDCXO\_CTRL.dcxo\_stream\_mode = 1

Use only LSB byte of "jDCXO\_DATA" as a streaming window. It requires to disable I<sup>2</sup>C register address autoincrement by writing "bI2C\_INC\_DIS" = 1 to allow DCXO offset updates in a very long I<sup>2</sup>C transaction, which is feeding only data bytes to the same register address.

## 4. Data application:

Absolute mode: bDCXO\_CTRL.dcxo\_rel\_mode = 0 Apply the input offset value directly as a frequency offset.

Relative mode: bDCXO\_CTRL.dcxo\_rel\_mode = 1

Apply the input offset value as a relative change from the current DCXO frequency offset in the internal 32-bit register, different from the jDCXO\_DATA" input register. This allows applying only incremental steps to move the internal frequency offset.

A DCXO register description in Figure 5.6 and t

Figure 5.6: DCXO control and data processing

#### 5.9 I<sup>2</sup>C Register Reference

The I<sup>2</sup>C interface is a byte-oriented interface. Registers are wider than 8 bits requiring to be split into multiple bytes located on subsequent register addresses. There are two types of multi byte registers:

- 1. Array of arrays, prefix **ab**, for example abUSER\_ID[4] are organized in little endian fashion, byte abUSER\_ID[0] is located at the lowest address, and the last byte of the array abUSER\_ID[3] is located at the highest address.

- 2. An assigned 32-bit long integer, prefix **j**, and a 32-bit IEEE 754-2008 floating point number, prefix **f** are organized in big endian fashion, such that the most significant byte (MSB) is located at the lowest address.

Any unassigned byte registers have prefix b. Registers in the I<sup>2</sup>C address space 0x00...0xFF without specifications in the register description table are reserved for factory use. All register bit fields labeled <reserved> are read only and are reserved for factory use. Read value should be ignored. Any register bits not specifically mentioned in "Bits" columns are unused. Writing to these registers is ignored and a read always returns a 0. Numerical values are either hexadecimal with 0x prefix or decimal without any prefix.

Descriptions of register table columns:

| Register              | Description                                                                                                                                                                                                 |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Addr                  | I <sup>2</sup> C register address.                                                                                                                                                                          |

| Register              | Register name.                                                                                                                                                                                              |

| Bytes                 | Number of bytes in the register. Wider than single byte registers span several subsequent bytes in an address space.                                                                                        |

| Endian                | Endian for registers wider than one byte. Not applicable for single byte registers.                                                                                                                         |

| В                     | Big endian. The most significant byte (MSB) of the register appears at the lowest address.                                                                                                                  |

| L                     | Little endian. The least significant byte (LSB) of the register appears at the lowest address.                                                                                                              |

| Field                 | Field name within the register.                                                                                                                                                                             |

| <reserved></reserved> | Reserved for factory use and readable only                                                                                                                                                                  |

| Bits                  | Field bit locations within a register. When the field spans more than one bit, the [M:L] notate. Denoting locations of a most significant bit M and a least significant bit L within the register are used. |

| Туре                  | Field access type.                                                                                                                                                                                          |

| R/W                   | Read/write field by I <sup>2</sup> C.                                                                                                                                                                       |

| R                     | Read only field by I <sup>2</sup> C.                                                                                                                                                                        |

| W1                    | Writing a 1 triggers an associated event, while writing a 0 has no effect. A read always returns 0.                                                                                                         |

| Rst                   | Field reset value. The value 'Factory' indicates that the value depends on the individual device factory configuration.                                                                                     |

Table 5.4: I<sup>2</sup>C control registers summary

| Register                       | Addr         | Bytes | Endian   | Field                          | Bits             |

|--------------------------------|--------------|-------|----------|--------------------------------|------------------|

| bl2C_DEV_ID                    | 0x00         | 1     | Elidiali | i2c_dev_id                     | [7:0]            |

| bl2C_DERIV_ID                  | 0x01         | 1     |          | i2c_deriv_id                   | [7:0]            |

| bl2C_ANA_ID                    | 0x02         | 1     |          | i2c_ana_id                     | [7:0]            |

| bl2C_SYS_ID                    | 0x03         | 1     |          | i2c_sys_id                     | [7:0]            |

| bl2C_INC_DIS                   | 0x06         | 1     |          | i2c_sys_id<br>i2c_inc_dis      | [0]              |

| abUSER_REG[4]                  | 0x07         | 4     |          | user_reg                       | [31:0]           |

| bUDRV_CTRL                     | 0x0b         | 1     |          | udrv_oe_stop                   | [0]              |

| BODKV_CTKL                     | OXOD         | '     |          | udrv_run                       | [1]              |

| FDEV I DIO                     | 00-          |       |          |                                |                  |

| bDEV_LDIS                      | 0x0c         | 1     |          | <reserved></reserved>          | [0]              |

|                                |              |       |          |                                | [4]              |

|                                |              |       |          | dcxo_ldis                      | [6]              |

|                                |              |       |          | <reserved></reserved>          | [7]              |

| bDRV_LDIS                      | 0x0d         | 1     |          | drv_cmos_clkp_ldis             | [0]              |

|                                |              |       |          | drv_cmos_clkm_ldis             | [1]              |

|                                |              |       |          | drv_diff_ldis                  | [2]              |

| bDCXO_SYNC                     | 0x1a         | 1     |          | dcxo_stream_sync               | [0]              |

|                                |              |       |          | dcxo_clr_sec                   | [1]              |

|                                |              |       |          | dcxo_sat_neg                   | [6]              |

|                                |              |       |          | dcxo_sat_pos                   | [7]              |

| bDCXO_SHIFT                    | 0x1b         | 1     |          | dcxo_shift                     | [4:0]            |

| bDCXO_CTRL                     | 0x1c         | 1     |          | dcxo_size                      | [2:0]            |

|                                |              |       |          | dcxo_stream_mode               | [4]              |

|                                |              |       |          | dcxo_rel_mode                  | [5]              |

|                                |              |       |          | dcxo_ena                       | [6]              |

|                                |              |       |          | dcxo_clr                       |                  |

| :DOVO DATA                     | 0.44         |       | <u> </u> |                                | [7]              |

| jDCXO_DATA                     | 0x1d         | 12    | В        | dcxo_data                      | [31:0]           |

| abFACT_ID[12]                  | 0x21<br>0x2d |       | L        | fact_id                        | [95:0]           |

| abCFG_ID[6]                    | 0x2d<br>0x33 | 6 4   | L        | cfg_id                         | [47:0]           |

| abUSER_ID[4]<br>abUSER_INFO[2] | 0x33<br>0x37 | 2     | L        | user_id                        | [31:0]<br>[15:0] |

| bDRV_CFG                       | 0x3b         | 1     | L        | user_info                      |                  |

| bDRV_CFG                       | UXSD         | '     |          | drv_stop_hiz drv_cmos_high_str | [0]              |

|                                |              |       |          |                                | [1]              |

|                                |              |       |          | drv_cmos_slew                  | [3:2]            |

|                                |              |       |          | drv_cmos_clkp_inv              | [4]              |

|                                |              |       |          | drv_cmos_clkm_inv              | [5]              |

| bODIV_CTRL                     | 0x3c         | 1     |          | odiv_oe_ena                    | [0]              |

| bVC_LPF_BW_DIR                 | 0x41         | 1     |          | vc_lpf_bw_dir                  | [2:0]            |

| bVC_LPF_ABS_SAT                | 0x42         | 1     |          | vc_lpf_abs_sat                 | [7:0]            |

| bVC_VCTRL                      | 0x43         | 1     |          | vc_vctrl_dis                   | [0]              |

| bPADV_DIR_DATA                 | 0x44         | 1     |          | padv_dir_data                  | [7:0]            |

| bGPIO_PUP_ENA                  | 0x45         | 1     |          | gpio_pup_ena                   | [5:0]            |

| bGPIO_PDWN_ENA                 | 0x46         | 1     |          | gpio_pdwn_ena                  | [5:0]            |

| bGPIO_PULL5K_ENA               | 0x47         | 1     |          | gpio_pull5k_ena                | [5:0]            |

| bDRV_MODE                      | 0x54         | 1     |          | drv_mode                       | [7:0]            |

| fUSER_FREQ                     | 0x55         | 4     | В        | user_freq                      | [31:0]           |

| bUSYS_CTRL                     | 0x59         | 1     |          | usys_ctrl                      | [7:0]            |

| bUSYS_STAT                     | 0x5a         | 1     |          | stat_ready                     | [0]              |

|                                |              |       |          | stat_active                    | [1]              |

|                                |              |       |          | stat_tune<br>stat_rst          | [2]              |

|                                |              |       |          | stat_tran                      | [4]              |

|                                |              |       |          | stat_busy                      | [7]              |

|                                |              |       | 1        | 1 2.5                          | L · J            |

# Table 5.5: Factory device identification

| Register      | Addr | Field        | Bits  | Туре | Rst     | Description               |

|---------------|------|--------------|-------|------|---------|---------------------------|

| bl2C_DEV_ID   | 0x00 | i2c_dev_id   | [7:0] | R    | 0x84    | Device identification     |

| bl2C_DERIV_ID | 0x01 | i2c_deriv_id | [7:0] | R    | Factory | Derivative identification |

| bl2C_ANA_ID   | 0x02 | i2c_ana_id   | [7:0] | R    | Factory | Analog identification     |

| bl2C_SYS_ID   | 0x03 | i2c_sys_id   | [7:0] | R    | Factory | System identification     |

## Table 5.6: I<sup>2</sup>C address autoincrement control

| Register     | Addr | Field       | Bits | Туре | Rst | Description                                                                                                                                                                                                                     |

|--------------|------|-------------|------|------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bl2C_INC_DIS | 0x06 | i2c_inc_dis | [0]  | R/W  | 0   | Disable automatic I <sup>2</sup> C register address increment. If this bit is set the automatic I <sup>2</sup> C register address increment after each write or a                                                               |

|              |      |             |      |      |     | read data is disabled. This is useful in situations when the user wants to repeatedly read a same address location. For example, monitoring some status bit or using the DCXO feature in a single I <sup>2</sup> C transaction. |

# Table 5.7: User scratch pad byte array

| Register      | Addr | Field    | Bits   | Туре | Rst | Description                                            |

|---------------|------|----------|--------|------|-----|--------------------------------------------------------|

| abUSER_REG[4] | 0x07 | user_reg | [31:0] | R/W  | 0   | User scratch pad R/W byte array. Controls no hardware. |

# Table 5.8: Output driver user control

| Register   | Addr | Field        | Bits | Type | Rst | Description                                                                                                                                                                                               |

|------------|------|--------------|------|------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bUDRV_CTRL | 0x0b | udrv_oe_stop | [0]  | R/W  | 0   | Stop the output driver. This bit is an inverse of the enabling the output driver bit "bODIV_CTRL.odiv_oe_ena". An active high control bit disables the output driver.                                     |

|            |      | udrv_run     | [1]  | R    | 0   | Status bit of the output driver. Read only. If 1, then the device actively generates signal to the output driver. Output driver then can be enabled or disabled to propagate its input signal to outputs. |

## Table 5.9: Feature lock or disable status

| Register  | Addr | Field                 | Bits | Туре | Rst     | Description                                                   |

|-----------|------|-----------------------|------|------|---------|---------------------------------------------------------------|

| bDEV_LDIS | 0x0c | <reserved></reserved> | [0]  | R    | Factory | Reserved for factory use.                                     |

|           |      | <reserved></reserved> | [4]  | R    | Factory | Reserved for factory use.                                     |

|           |      | dcxo_ldis             | [6]  | R    | 0       | DCXO feature status. If the bit is 1 then the DCXO feature is |

|           |      |                       |      |      |         | factory blocked and cannot be enabled.                        |

|           |      | <reserved></reserved> | [7]  | R    | Factory | Reserved for factory use.                                     |

| bDRV_LDIS | 0x0d | drv_cmos_clkp_ldis    | [0]  | R    | 0       | CMOS CLK+ half of CMOS driver is factory disabled.            |

|           |      | drv_cmos_clkm_ldis    | [1]  | R    | 0       | CMOS CLK- half of CMOS driver is factory disabled.            |

|           |      | drv_diff_ldis         | [2]  | R    | 0       | Differential output driver is factory disabled.               |

Table 5.10: DCXO control

| Register    | Addr | Field            | Bits  | Type | Rst | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-------------|------|------------------|-------|------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bDCXO_SYNC  | 0x1a | dcxo_stream_sync | [0]   | W1   | 0   | Writing a 1 to this bit clears the streaming mode synchronization logic. The next write to the bDCXO_DATAL register byte is treated as the MSB byte of the burst. This bit allows to forcibly synchronize the streaming operation when in doubt.  Note that any write to bDCXO_CTRL register also clears the streaming mode synchronization logic.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|             |      | dcxo_clr_sec     | [1]   | W1   | 0   | Secondary duplicated clear pulse bit for user convenience, same function as bDCXO_CTRL.dcxo_clr bit. See the bDCXO_CTRL description.  The clear affects only the DCXO data processing and not the DCXO I²C control registers. All the current DCXO settings as set in bDCXO_CTRL and bDCXO_SHIFT registers stay intact.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|             |      | dcxo_sat_neg     | [6]   | R    | 0   | If 1, then DCXO frequency deviation internal value has saturated to minimum negative value. Register bit updated every time when the 32-bit DCXO internal value is updated. The bit is not sticky. Cleared by bDCXO_SYNC.dcxo_clr_sec = 1 or bDCXO_CTRL.dcxo_clr = 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|             |      | dcxo_sat_pos     | [7]   | R    | 0   | If 1, then DCXO frequency deviation internal value has saturated to maximum positive value. Register bit updated every time the 32-bit DCXO internal value is updated. The bit is not sticky. Cleared by bDCXO_SYNC.dcxo_clr_sec = 1 or bDCXO_CTRL.dcxo_clr =1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| bDCXO_SHIFT | 0x1b | dcxo_shift       | [4:0] | R/W  | 0   | Number of bits to shift the input jDCXO_DATA value to the left before internal processing. The left bit shift is always applied at the input DCXO value in all modes and configurations. The shift value is in the range of <0, 24> bits. If the shift number is greater than 24, then it is internally forced to 24.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| bDCXO_CTRL  | 0x1c | dcxo_size        | [2:0] | R/W  | 0   | Number of streamed bytes per input value or number of bottom jDCXO_DATA bytes to be used as input value in direct register access mode. The valid values are 0, 1, 2, 3, and 4 bytes. Default value 0 is an alias of value 4. The value greater than 4 is internally forced to 4.  All values are internally sign-extended to 57 bits before the value is used. The bDCXO_SHIFT left shift is applied on the internally sign-extended 57-bit number.  For streamed mode the number denotes the size of ordered byte burst in the I²C transaction:  4 {H M N L} 32 bits, the last L byte is always LSB byte  3 {M N L} 16 bits  1 {L} 8 bits  For direct register mode, this number denotes the number of LSB bytes from the jDCXO_DATA. It is used to form a number to be internally sign-extended to 57 bits. The number of bytes and their order is the same as in the streaming table above.  The {H} denotes the MSB byte at byte address jDCXO_DATA while the {L} denotes the LSB byte at the byte address jDCXO_DATA is a 32-bit signed integer stored in a big endian fashion. MSB is at lower address. The bDCXO_DATAL byte at byte address jDCXO_DATA + 3 is always the LSB byte for all widths and could be viewed as the value alignment anchor. |

|             |      | dcxo_stream_mode | [4]   | R/W  | 0   | DCXO frequency offset value input mode.  0 regular direct register mode.  For situations when I <sup>2</sup> C address autoincrement is active (default mode), the jDCXO_DATA four byte array can be written any time. Whenever the bDCXO_DATAL location at the jDCXO_DATA + 3 byte address is written, the number of bytes is selected by bDCXO_CTRL.dxco_size number is taken from the bottom of the jDCXO_DATA value, aligned towards bDCXO_DATAL location as LSB byte. Those selected bytes are sign-extended to 57 bits and left shifted by the bDCXO_SHIFT value. The resulting number is then either used to add to the existing internal DCXO value in 57 bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Register   | Addr | Field         | Bits   | Туре | Rst | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|------------|------|---------------|--------|------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            |      |               |        |      |     | addition, thus the sum is then sign saturated to bottom 32 bits to be used as a new DCXO value, or the value is sign saturated to 32 bits to be used directly as the new DCXO value.  1 streaming mode. For situations when I²C register address autoincrement is disabled, user must write a register bl2C_INC_DIS = 1 to actively disable the I²C register address autoincrement. The setting is global and applies to all I²C register accesses, not only to the DCXO data registers. The user must choose to stream 4 {H M N L}, 3 {M N L}, 2 {N L}, or 1 {L} byte by setting the bDCXO_SIZE register before starting streaming operation. The stream byte order is from left to right and the LSB is always come last in the value burst. All data is written to bDCXO_DATAL register only. Writing to other jDCXO_DATA register bytes are ignored. The streamed byte value is then treated the same way as in the regular direct register mode described above. The streaming mode is useful for very fast DCXO value updates, possibly in a single and very long I²C transaction. |

|            |      | dcxo_rel_mode | [5]    | R/W  | 0   | DCXO frequency offset value usage mode.  0 absolute mode. The user signed DCXO input value obtained using the current access mode is sign-extended to 57 bits and then left shifted by bDCXO_SHIFT bits. The shifted signed value is sign-saturated to bottom 32 bits and used as the internal DCXO frequency offset value.  1 relative mode. The user signed DCXO input value obtained using the current access mode is sign-extended to 57 bits and then left shifted by bDCXO_SHIFT bits. The shifted signed value is added to the current internal 32-bit DCXO value resulting in 57-bit internal signed addition number. The signed 57-bit sum is sign saturated to bottom 32 bits and then used as the internal DCXO frequency offset value.  If the bottom 32-bit saturation happened, the read only saturation flags bDCXO_SYNC.dcxo_sat_pos and bDCXO_SYNC.dcxo_sat_neg reflect the saturation operation of the last update of the internal DCXO frequency offset value.                                                                                                        |

|            |      | dcxo_ena      | [6]    | R/W  | 0   | Enable the DCXO operation.  If this bit is 1, then the DCXO operation is enabled.  If this bit is 0, then the DXCO operation is disabled. All control bits in bDCXO_CTRL register are ignored with an exception of bDCXO_CTRL.dcxo_clr, which can be written as 1 to clear DCXO processing module.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|            |      | dcxo_clr      | [7]    | W1   | 0   | Writing 1 to this bit clears all the DCXO internal frequency offset value registers, all DCXO value holding registers, and streaming mode synchronization logic. All mentioned registers are cleared even if bDCXO_CTRL.dcxo_ena = 0. The clear does not affect bDCXO_SHIFT register.  Note that the streaming mode synchronization logic is cleared every time the bDCXO_CTRL register is written, even if the bDCXO_CTRL.dcxo_ena = 0 or bDCXO_CTRL.dcxo_clr = 0. It is highly recommended that this bit is written as 1 when the DCXO is being enabled by setting bDCXO_CTRL.dcxo_ena = 1 to clear the internal processing registers.                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| jDCXO_DATA | 0x1d | dcxo_data     | [31:0] | R/W  | 0   | DCXO data register through which the actual signed 32 bit DCXO control data is applied. Increasing value increases the output frequency. The 32-bit input value represents 11.21s signed 2's complement number in [0.9536743164 ppm] units as deviation from current central frequency.  The 4 register bytes can be viewed separately as bDCXO_DATAH, bDCXO_DATAM, bDCXO_DATAN, and bDCXO_DATAL data bytes and writing to them depends on the write mode selected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Register | Addr | Field    | Bits | Type | Rst | Description                                                                                                       |

|----------|------|----------|------|------|-----|-------------------------------------------------------------------------------------------------------------------|

|          |      |          |      |      |     | bDCXO_DATAH jDCXO_DATA address + 0                                                                                |

|          |      |          |      |      |     | bDCXO_DATAM jDCXO_DATA address + 1                                                                                |

|          |      |          |      |      |     | bDCXO_DATAN jDCXO_DATA address + 2                                                                                |

|          |      |          |      |      |     | bDCXO_DATAL jDCXO_DATA address + 3 always LSB                                                                     |

|          |      |          |      |      |     |                                                                                                                   |

|          |      |          |      |      |     | The bDCXO_DATAL LSB byte refers to the jDCXO_DATA[7:0]                                                            |

|          |      |          |      |      |     | bits, which is the byte at the highest address (jDCXO_DATA                                                        |

|          |      |          |      |      |     | address + 3) since the register value is represented in big                                                       |

|          |      |          |      |      |     | endian. MSB is at lower address. There are holding registers                                                      |

|          |      |          |      |      |     | for 3 MSB upper value bytes and the written value will get                                                        |

|          |      |          |      |      |     | applied internally only if the bDCXO_DATAL byte is written.                                                       |

|          |      |          |      |      |     | In a regular direct register access mode,                                                                         |

|          |      |          |      |      |     | bDCXO_CTRL.dcxo_stream_mode = 0, any byte in the 4-                                                               |

|          |      |          |      |      |     | byte jDCXO_DATA register can be written at any time. The                                                          |

|          |      |          |      |      |     | most convenient way is to write it as a burst of bytes with                                                       |

|          |      |          |      |      |     | incrementing byte address after each byte write. The written                                                      |

|          |      |          |      |      |     | value is applied internally only after the last bDCXO_DATAL                                                       |